Compute Express Link (CXL) emerges as an innovative technological solution addressing critical memory wall challenges in modern computing infrastructures. The interconnect technology presents a comprehensive approach to overcoming existing memory architecture limitations, offering high bandwidth density and a standardized interface for memory expansion and pooling. CXL’s innovative design has attracted substantial attention from both industrial and academic domains, signaling its potential to transform data center architectures fundamentally. Major technology leaders, including Intel, Samsung, and SK Hynix, are actively exploring and implementing CXL technologies. The technology’s significance extends beyond mere incremental improvements, promising to revolutionize how computational systems manage and utilize memory resources in increasingly complex computing environments.

Despite CXL’s promising technological framework, the technology confronts significant performance challenges arising from external interference within server architectures. The interconnect technology faces potential performance threats from complex interactions between Main Memory (MMEM) and neighboring storage components, which current research has not comprehensively examined. Maintaining performance isolation becomes critical, especially for applications with stringent performance requirements. Existing research, such as the MT2 study, has attempted to explore interference between persistent memory and DRAM by identifying noisy neighbors and mitigating memory traffic disruptions. However, CXL-specific interference mechanisms remain largely understudied. Current simulation approaches typically introduce delay factors manually, failing to accurately reflect real-world operational environments and the nuanced interactions between different computational components.

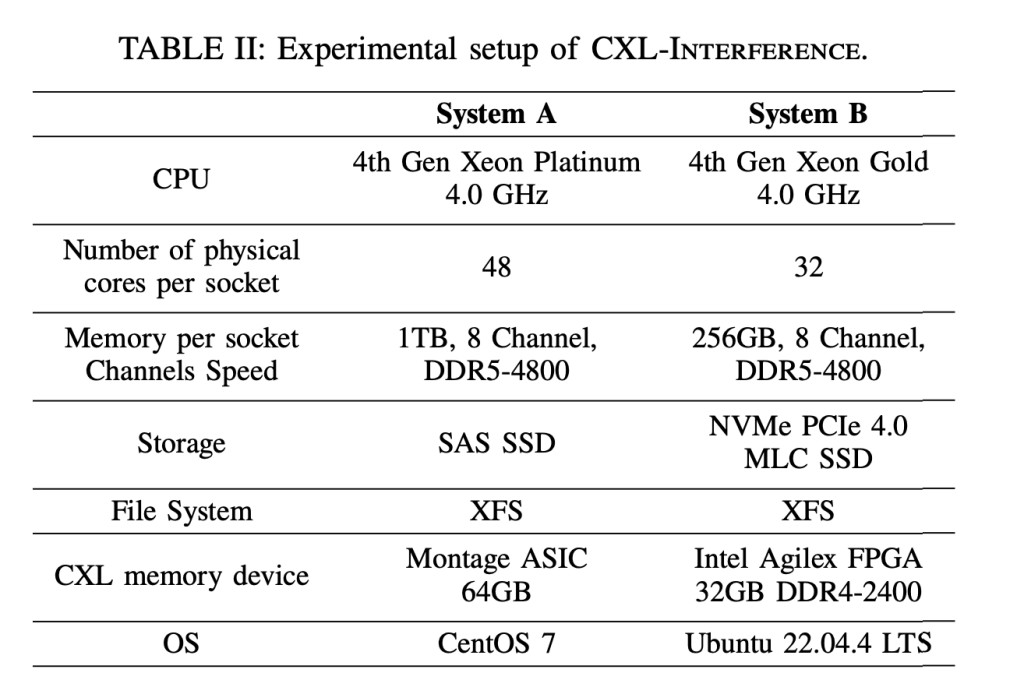

Researchers from Tsinghua University, the Institute of Computing Technology, the Chinese Academy of Sciences, Alibaba Group, and Zhejiang University developed CXL-Interference, a comprehensive methodology to systematically characterize and analyze potential interference mechanisms between memory and storage systems in CXL architectures. The study employed configurable microbenchmarks and real-world applications across two distinct CXL hardware configurations to identify and explore interference conditions. By conducting detailed evaluations using kernel functions and hardware performance counters, the research team investigated interference scenarios across multiple application domains, including file systems, databases, machine learning, large language models, in-memory databases, and graph computing. Importantly, the study pioneered the first real-device investigation of CXL interference, demonstrating a novel approach to understanding complex computational interactions. The research successfully explored software and hardware intervention strategies, ultimately developing solutions to restore memory bandwidth to 99% of its original performance levels.

CXL, developed in 2019, represents a robust and unique open standard interconnect designed to enhance data-centric application performance through high-speed, low-latency communication between computational components. The technology’s protocol stack comprises three critical elements: CXL.io, CXL.cache, and CXL.mem, each facilitating distinct data transmission and memory access mechanisms. CXL devices are categorized into three types, with varying capabilities ranging from communication facilitation to memory resource sharing and expansion. These devices can be implemented using FPGA or ASIC technologies, with vendors like Intel, Samsung, Montage, and Micron actively developing innovative solutions. The technology addresses fundamental limitations in traditional memory systems, particularly the constrained capacity and bandwidth of conventional DRAM, by offering sophisticated memory pooling and expansion capabilities.

The research team established comprehensive microbenchmarks to systematically evaluate CXL interference across multiple memory and storage operations. The experimental setup involved cross-evaluating three memory-related operations (load, store, and non-temporal store) and two storage-related operations (random-read and random-write). Researchers meticulously controlled experimental conditions by disabling hyperthreading, locking CPU frequency, and clearing the cache before each test. Experiments allocated main and interfering processes to separate cores within the same NUMA node, ensuring precise measurement accuracy. Multiple test iterations were conducted to obtain statistically reliable average results. The microbenchmark design allowed for a detailed exploration of interference mechanisms between CXL, MMEM, and storage systems, providing nuanced insights into performance interactions across different computational configurations.

The research investigation explored interference scenarios across four distinct application types, systematically categorizing them into Type A through Type D. These categories encompassed filesystem-related applications under CXL traffic, CXL-related applications under SSD traffic, MMEM-related applications under CXL traffic, and CXL-related applications under MMEM traffic. Researchers selected a diverse range of applications with varied computational characteristics to comprehensively analyze interference mechanisms. The study meticulously documented performance impacts across different scenarios. The analysis revealed consistent contention and interference patterns across multiple access types and system configurations, highlighting the complex interdependencies between computational components in modern server architectures.

As CXL technology transitions from theoretical concepts to commercially available devices, researchers recognize the critical need to examine these components beyond isolated characterizations. The study reveals significant performance implications when CXL devices interact with other system components, demonstrating potential performance drops of up to 93.2% under specific interference scenarios. By systematically investigating the root causes of these performance disruptions, the research not only highlights the complex interactions within modern computational architectures but also proposes targeted mechanisms to manage CXL traffic. The comprehensive evaluation provides crucial insights into the technological challenges and potential mitigation strategies for emerging memory and interconnect technologies, offering a nuanced understanding of the performance trade-offs inherent in next-generation computing infrastructures.

Check out the Paper. All credit for this research goes to the researchers of this project. Also, don’t forget to follow us on Twitter and join our Telegram Channel and LinkedIn Group. If you like our work, you will love our newsletter.. Don’t Forget to join our 60k+ ML SubReddit.

The post Characterizing and Mitigating Compute Express Link (CXL) Interference in Modern Memory Systems appeared first on MarkTechPost.

Source: Read MoreÂ

‘

‘